本系列主要介紹視頻編解碼芯片的設計,以HEVC視頻編碼標準為基礎,簡要介紹編解碼芯片的整體硬件架構設計以及各核心模塊的算法優化與硬件流水線設計。

本章首先介紹了熵編碼和熵解碼算法的基本原理,并給出其在HEVC標準中的基本流程。然后對熵編碼和熵解碼的相關子模塊進行VLSI設計,得出設計結果與對比。

概述

編碼器在經過預測、變換、量化、環路濾波之后產生了大量的待編碼數據,這些數據將統一送入熵編碼模塊進行最后的壓縮。熵編碼利用信息間的熵冗余,對于信息量大的用長碼流表示,信息量小的用短碼流表示,進而壓縮數據。

編碼分類

編碼分為定長編碼和變長編碼。定長編碼是將所有的帶編碼的信息都用同樣長短的編碼去代表。而變長編碼會根據信息熵冗余,頻繁出現的用短的編碼,不頻繁出現的用長的編碼。

二進制算法編碼

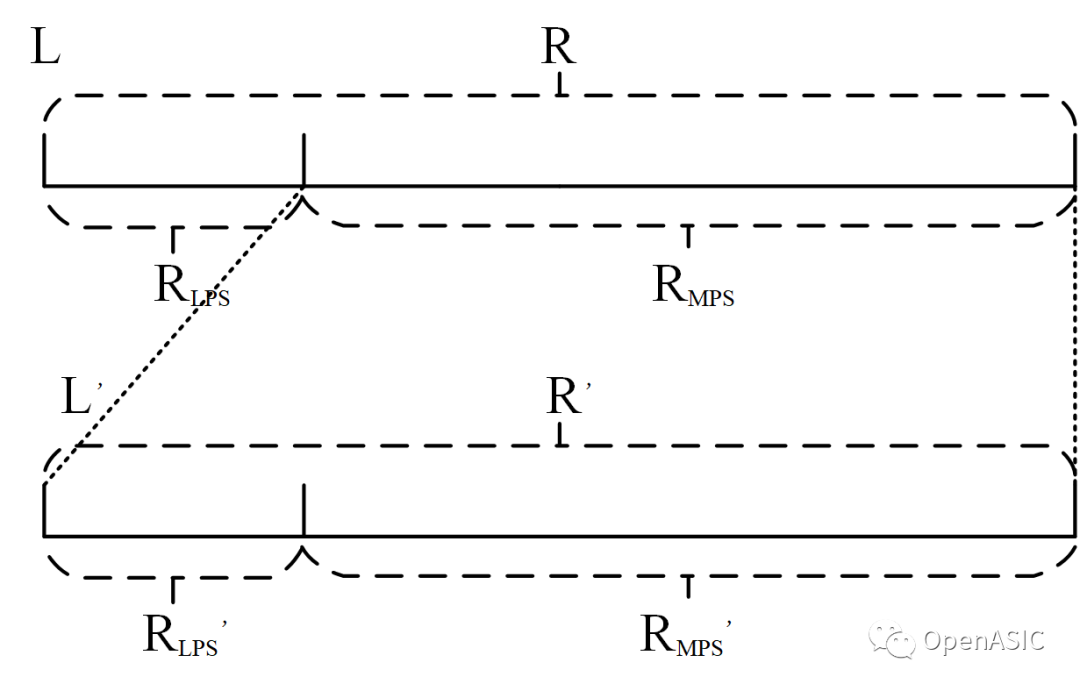

二進制算術編碼由算術編碼發展而來,但是涉及到的編碼對象只有二進制字符“0”和“1”,基本思想是用范圍0~1的小數概率區間表示一連串的輸入二進制序列。首先統計符號的概率分布,如下圖所示。其中MPS表示輸入二進制串中出現概率比較大的符號,LPS表示出現概率比較小的符號,R表示區間范圍,L表示區間下界,概率統計過程實際上表現為編碼區間不斷迭代子分。當下一個字符是MPS字符,那么新的區間范圍R’使用MPS的區間,其值??′=??×??M????。

HEVC中的熵編碼

HEVC標準中的上下文自適應二進制算術編碼(Context-based Adaptive Binary Arithmetic Coding, CABAC)對二進制算術編碼做了一些改進,使用了以下技術。

1)自適應二進制算術編碼

概率自適應更新直接計算過于復雜,在HEVC標準中將LPS概率區間進行離散化,離散區間為[0.01875,0.5],離散值一共64個,對應狀態轉換表如下表所示,表格第一行pStateIdx表示當前LPS字符概率量化后的值,第二行transIdxLPS表示輸入編碼字符為LPS字符時更新后的量化后的概率狀態,第三行transIdxMPS表示輸入編碼字符為MPS字符時更新后的量化后的概率狀態。

2)上下文模型

不同種類的輸入數據理應有不同的統計特性,因此熵編碼引入了上下文的概念。上下文模型將CABAC輸入的每個二進制符號進行分類,不同類的數據使用的上下文模型不同,獨立進行算術編碼的概率更新。

3)乘法優化

區間子分過程涉及到乘法,硬件開銷很大,因此在CABAC算法中將這一過程同樣優化為查找表,建立了一個64×4的表格,通過查表即可得到已經算好的乘法值。

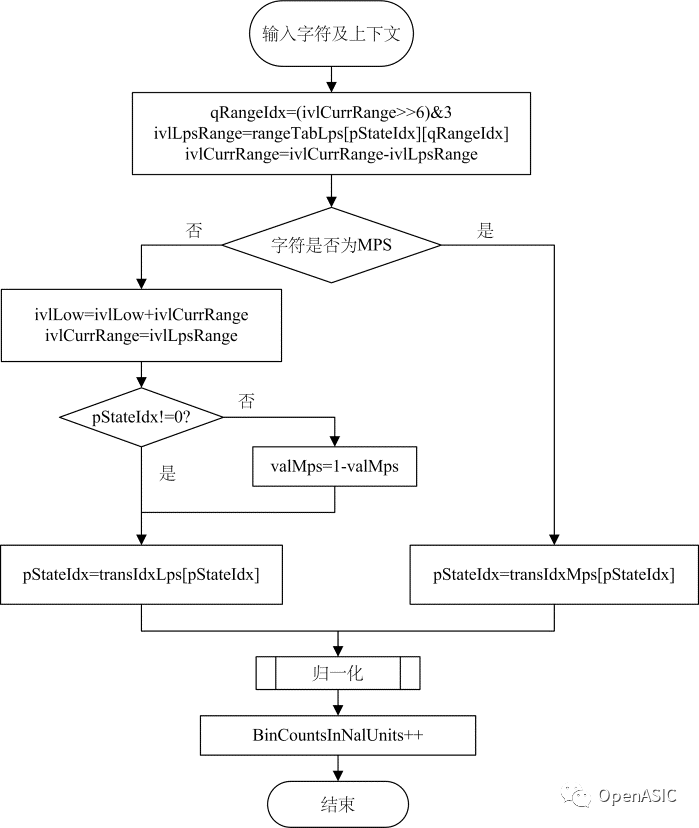

4)編碼字符分類

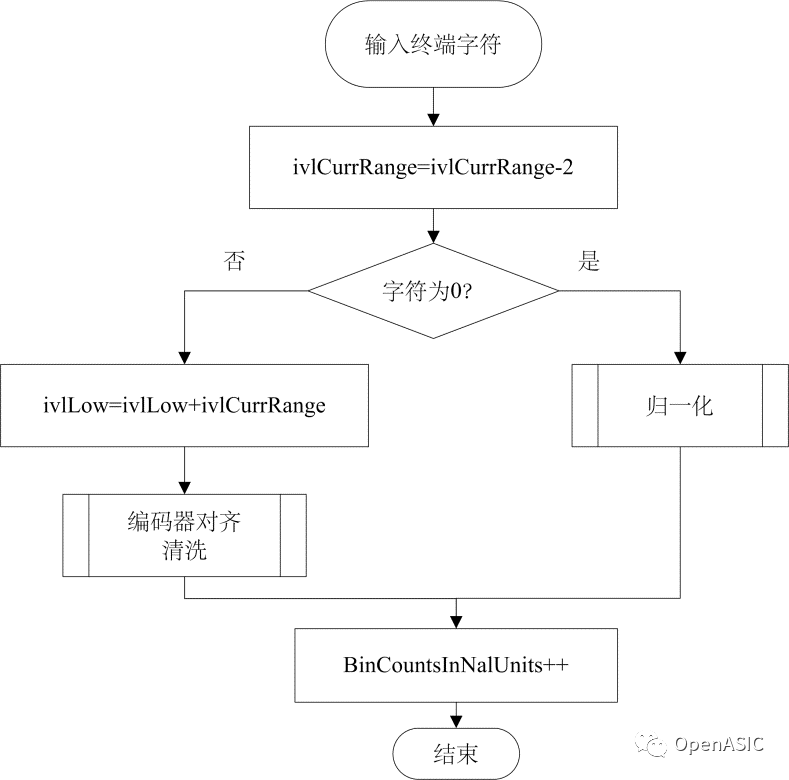

HEVC將編碼字符分為三類,第一類是常規模式(Regular Mode)字符,輸入不僅包括二進制字符,還需要當前字符的上下文模型,用于根據概率自適應更新編碼區間。首先根據當前上下文模型pStateIdx和編碼區間ivlCurrRange得到區間范圍,接著根據編碼字符是否為MPS字符進一步更新下界ivlLow值,最后更新上下文模型,歸一化重整區間,如下圖1所示。

圖1

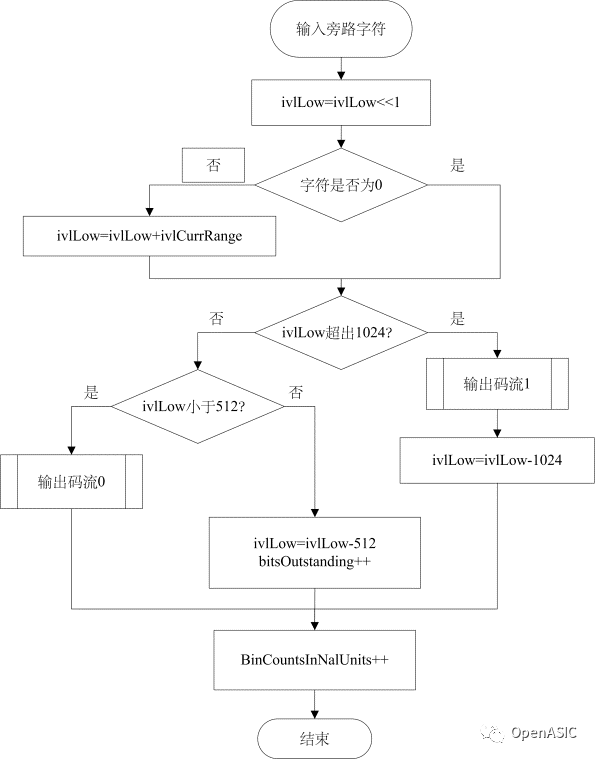

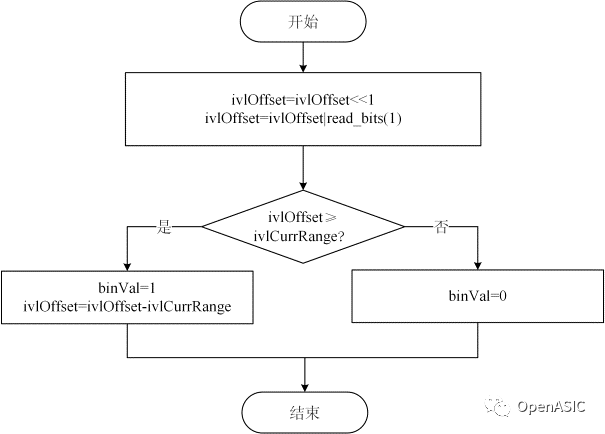

第二類是旁路模式(BypassMode)字符,固定初始LPS概率為0.5,不需要更新上下文,編碼流程較為簡單,如下圖2所示。

圖2

第三類是終端模式(TerminalMode)字符,僅編碼結束標志,當幀結束時需要將編碼器緩存的碼流全部移除并且需要字節對齊,因此這里有個額外的編碼器對齊清洗的過程,如下圖3所示。

圖3

HEVC中的熵解碼

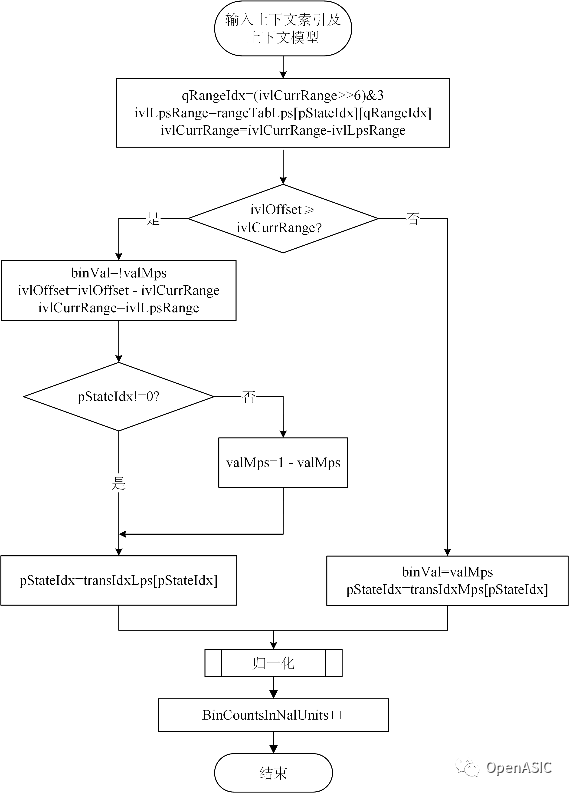

編碼過程將二進制字符分為旁路模式、常規模式和終端模式三種,熵解碼需要有相應的解碼引擎與其一一對應。常規解碼引擎流程圖4如下所示,對比常規模式編碼可以發現流程非常相似,區別在于編碼不僅需要知道上下文索引還需要輸入字符,而解碼只需要上下文模型及上下文索引。在初始化過程編碼與解碼完全相同,接著解碼判斷ivlOffset值與當前區間范圍ivlCurrRange的大小來確定解析出的編碼字符是MPS還是LPS。歸一化過程會判斷是否接著輸入1比特碼流。

圖4

旁路模式解碼引擎及終端模式解碼引擎流程圖如下圖5所示,可以看出相對較為簡單,且與常規模式解碼過程類似,關鍵判斷條件是ivlOffset與ivlCurrRange大小比較。

圖5

設計考量

熵編碼

熵編碼可分為四部分:“準備語法元素”、“二值化”、“更新上下文”和“算術編碼”。“準備語法元素”將熵編碼部分輸入的整個CTU的數據進行預處理,得到CABAC需要編碼的語法元素;“二值化”的作用是將語法元素變成二進制符號;“更新上下文”部分將每一種二進制符號進行概率統計;“算術編碼”部分將輸入的二進制串進行壓縮得到最終的碼流。

熵編碼主要存在以下設計難點:(1)處理流程復雜,狀態機設計復雜。(2)上下文模型更新存在數據依賴,這是一個串行的過程,使用同一上下文的bin需要等上下文更新后才能獲得其正確的上下文。(3)算術編碼存在數據依賴,算術編碼模塊由于要自適應迭代編碼區間,存在嚴重的數據依賴。

熵解碼

熵解碼也可分為四部分:“判斷語法元素”、“算術解碼”、“更新上下文”和“反二值化”。“判斷語法元素”部分按照標準中嚴格定義的編碼順序同步進行分析,得到當前需要解碼出哪一種語法元素。“算術解碼”部分先根據判斷語法元素給出的上下文模型種類查表得到上下文模型,根據上下文模型里的數據解碼引擎解析出當前解碼區間范圍Range和偏移量Offset,進一步得到解碼出的具體二進制字符。“更新上下文”根據解碼的二進制字符,上下文模型進行自適應更新以備下一次解碼使用。“反二值化”模塊將二進制字符還原為語法元素的真實值,至此一個語法元素解析完成。此語法元素會送回“判斷語法元素”模塊決定下一個語法元素的種類以及上下文模型的類型。

熵解碼過程前后存在著嚴重的數據依賴,主要表現在以下三個方面:(1)“判斷語法元素”與“反二值化”的數據依賴。(2)“更新上下文模塊”數據更新的依賴。(3)“算術解碼”模塊區間迭代的數據依賴。

熵編碼的VLSI設計

頂層架構

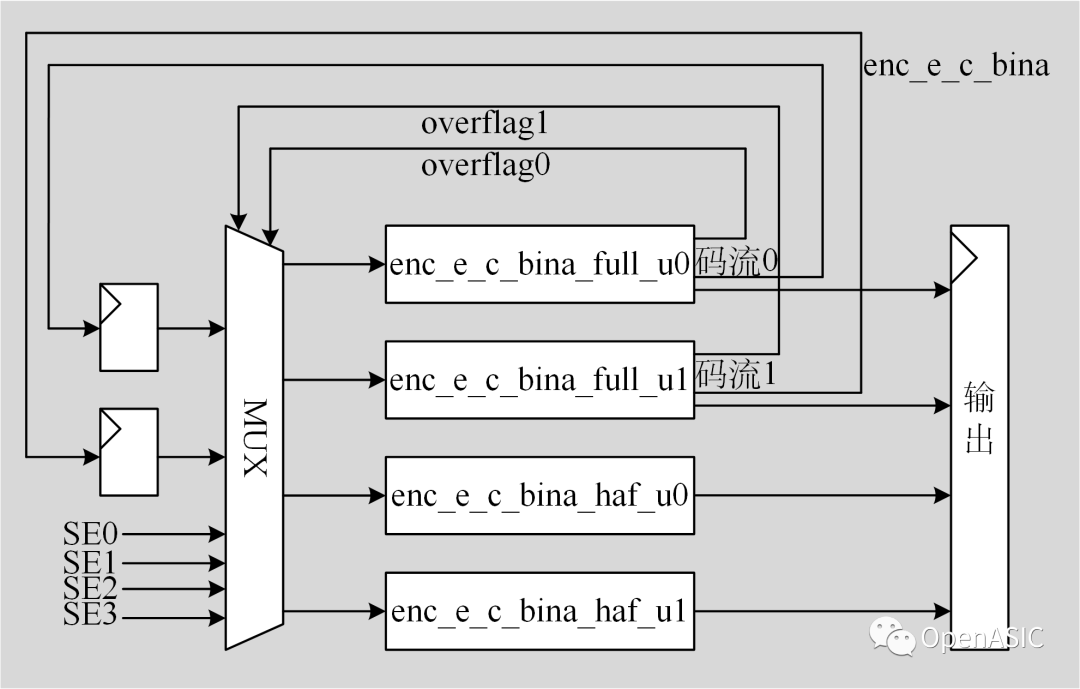

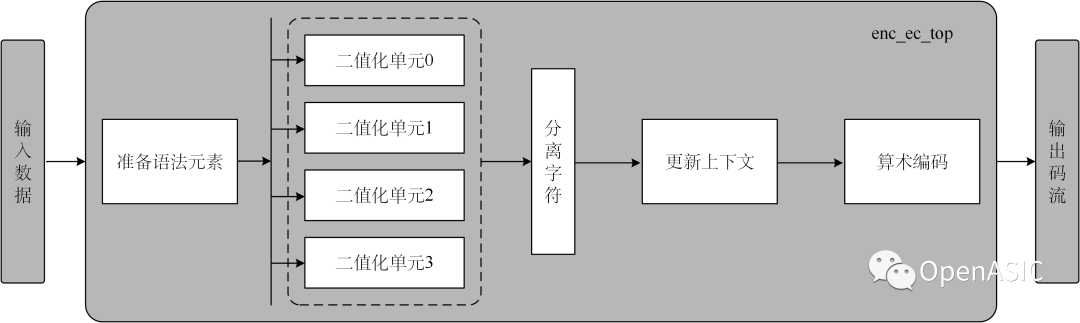

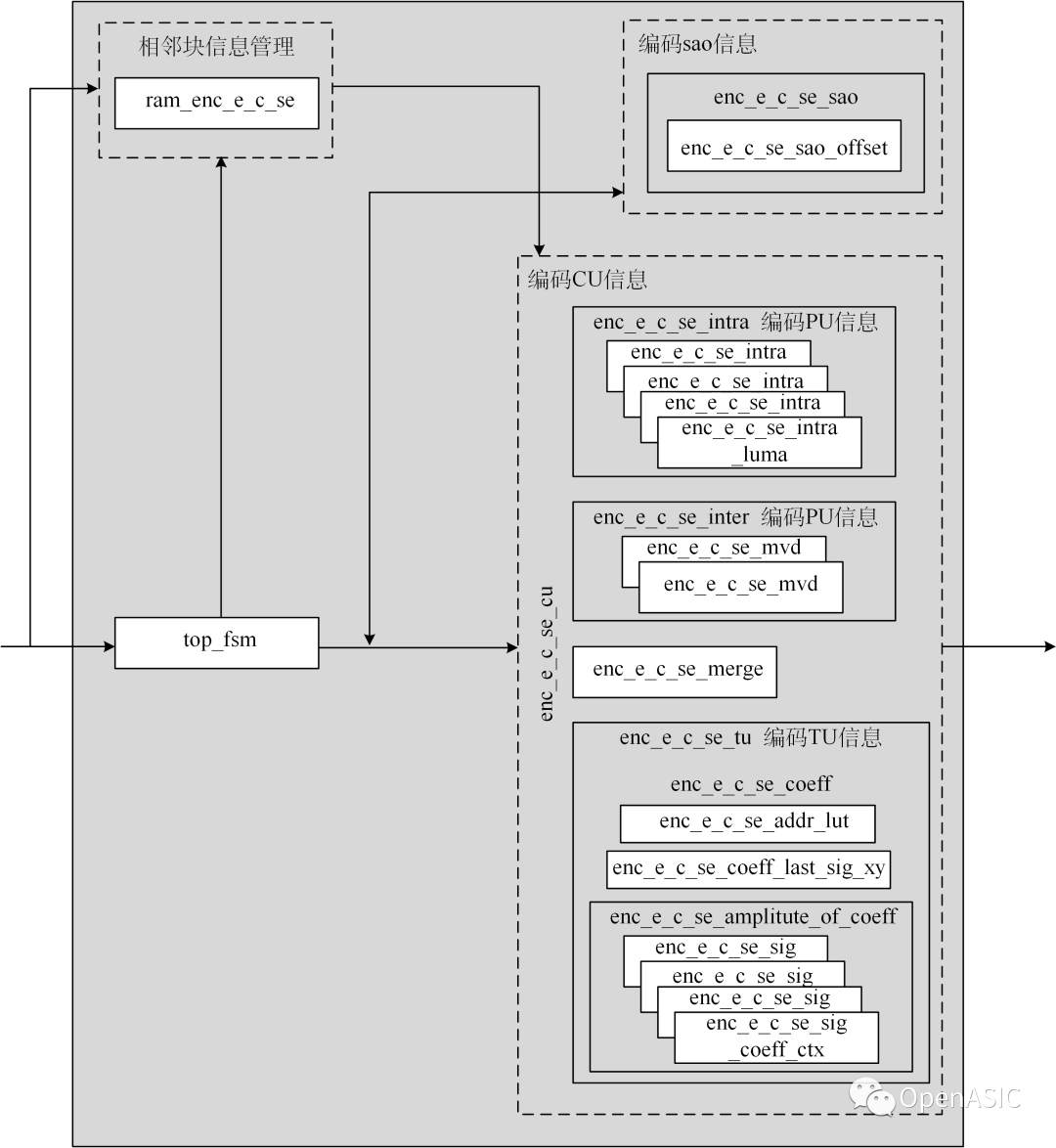

為了提高吞吐率,采用了深度流水的方式進行設計,并盡可能地提高并行度。具體表現為將準備語法元素、二值化、更新上下文和算術編碼獨立流水,語法元素的準備不依賴后續模塊的結果,因此可以深度流水化。對應架構圖如下圖6所示,分為了五個部分。

圖6

準備語法元素模塊

圖7

top_fsm是“準備語法元素”的頂層狀態機,對應了e_c部分最上層的處理邏輯:幀開始初始化->編碼SAO信息->根據劃分跳轉至第一個CU塊->循環遍歷所有CU->CTU編碼結束。

enc_e_c_se_sao模塊進行sao信息的編碼,輸入是62bit的sao數據,輸出是一堆需要編碼的語法元素,四個一組用于并行。

enc_e_c_se_cu模塊編碼當前CU的所有信息,因為CU中包含眾多數據待處理,這一部分同樣使用狀態機進行控制,控制邏輯為CU->PU->TU。

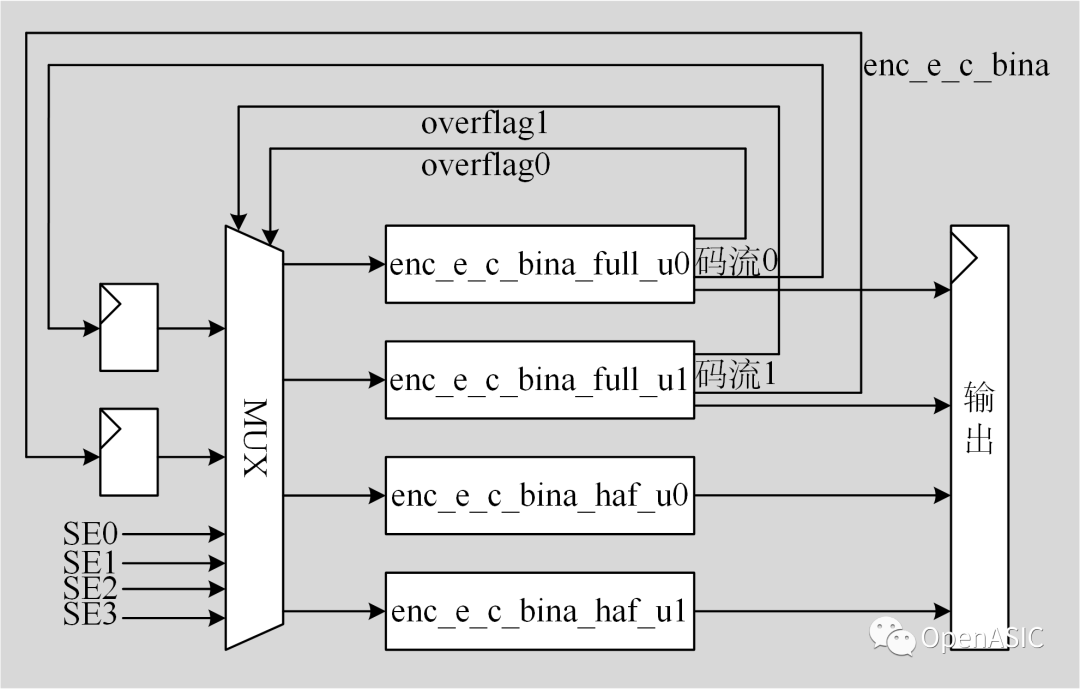

二值化模塊

二值化模塊將輸入的語法元素通過特定的編碼方式得到二進制串,同時此模塊將決定每個二進制字符最終的上下文模型。考慮到出現連續且大數值的殘差系數的場景,判斷其超出處理能力后可以先輸出前一半,隨后輸出后一半,將二值化分為兩步進行處理,同時“準備語法元素”模塊和此模塊間使用FIFO進行緩沖,二值化模塊結構圖8如下所示。

圖8

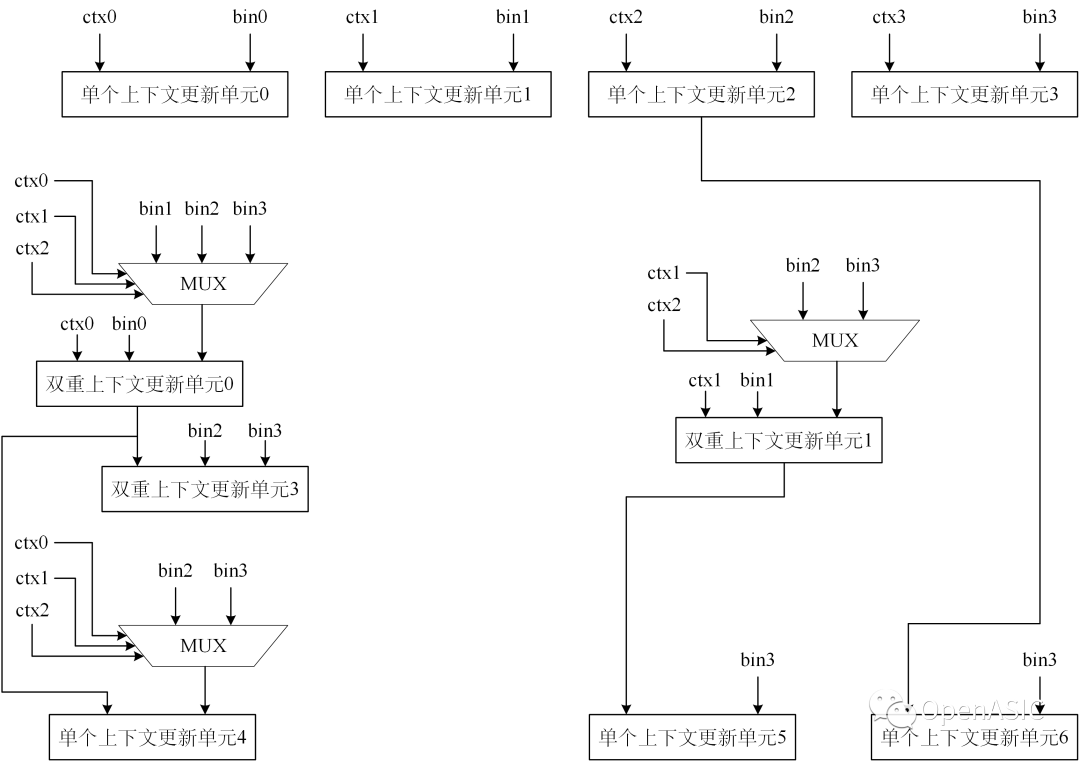

更新上下文模塊

更新上下文模塊對不同上下文模型進行獨立更新,此模塊最多同時更新四個上下文。參考文獻[1]的做法,引入雙重更新上下文單元,使用雙重狀態轉換表使得更新上下文時關鍵路徑最差情況下不再經過四次更新表格,而是兩個雙重查找表,能夠有效減小關鍵路徑。對應上下文模型更新模塊設計如下圖9所示,一共使用了七個單個更新上下文單元和三個雙重更新上下文單元,輸出經選擇器選擇即可得到準確的輸出。

圖9

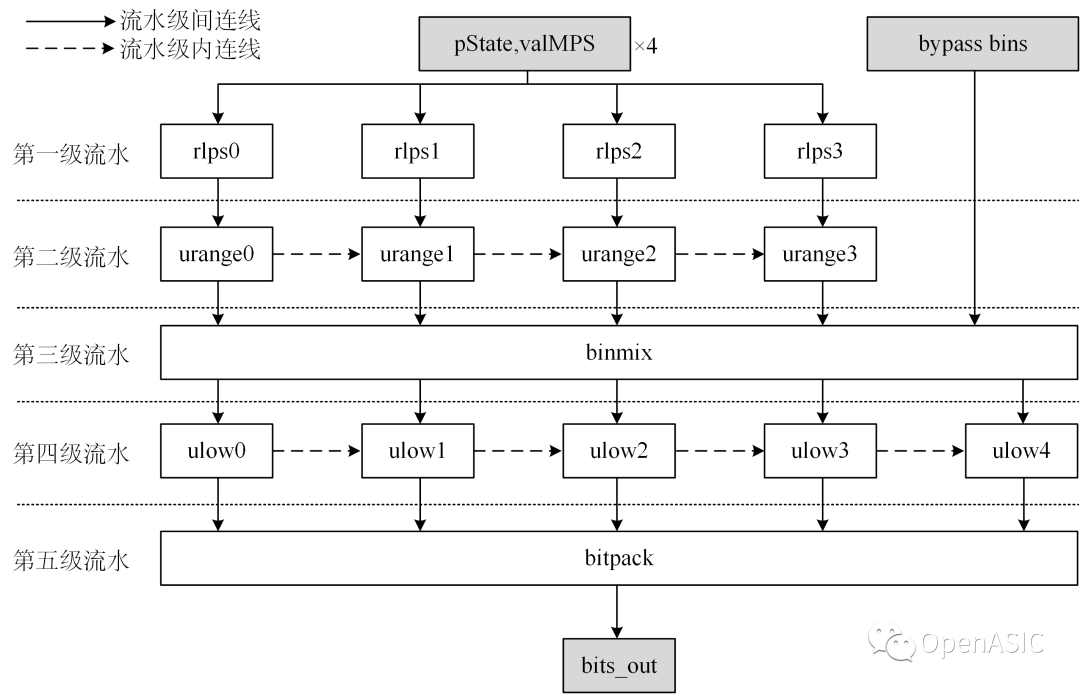

算數編碼模塊

典型的四路并行算術編碼結構如下圖所示,包含以下幾個子模塊:enc_e_c_rlps,根據表格rangeTabLps查找乘法結果;enc_e_c_urange,更新當前編碼的區間范圍;enc_e_c_binmix,由于引入了字符分離的技術,在這里要將所有的編碼字符合在一起;enc_e_c_ulow,更新當前編碼區間的下界;enc_e_c_ulow_refine,下界與區間范圍的整理,調整區間范圍至標準范圍,輸出溢出位;enc_e_c_bitpack,打包前級輸出的單bit 碼流,每一個byte 輸出一次。

圖10

性能評估

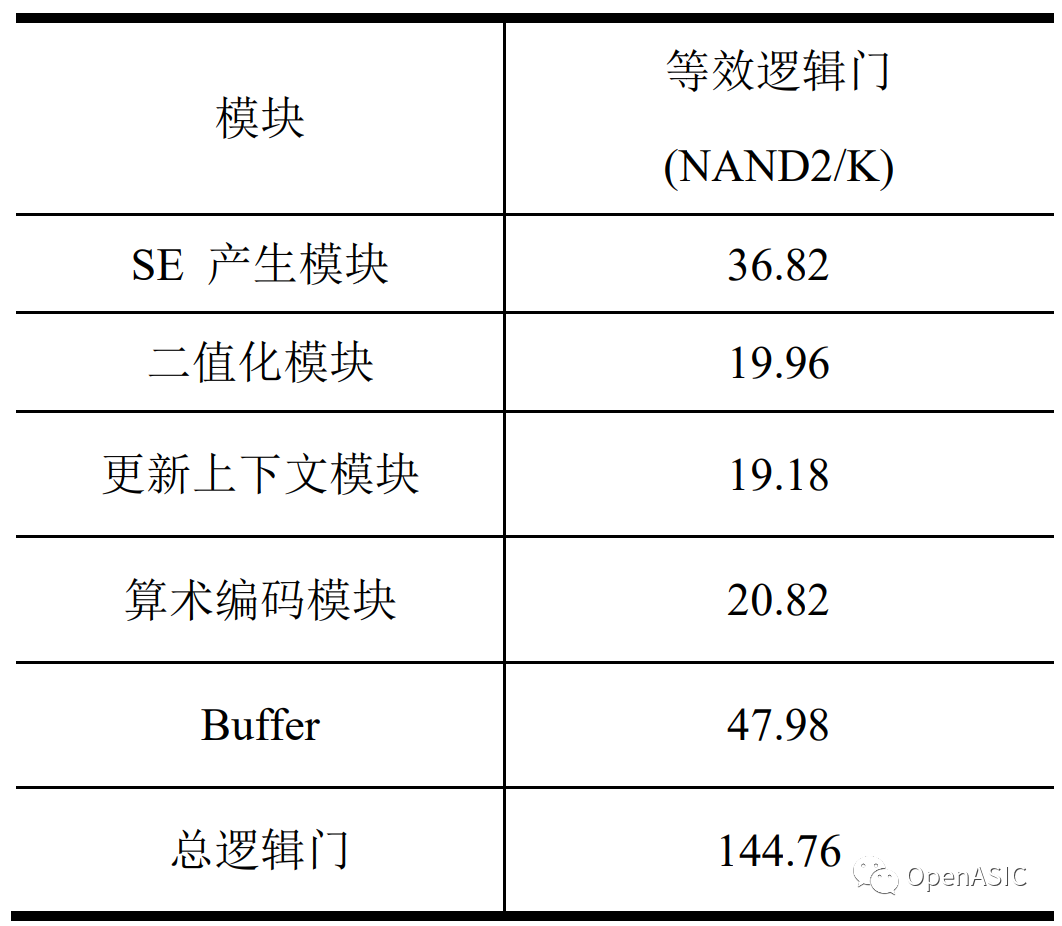

在TSMC65nm 工藝下基于頻率500M 對熵編碼進行綜合得到各主要模塊面積如下表1所示。

表1

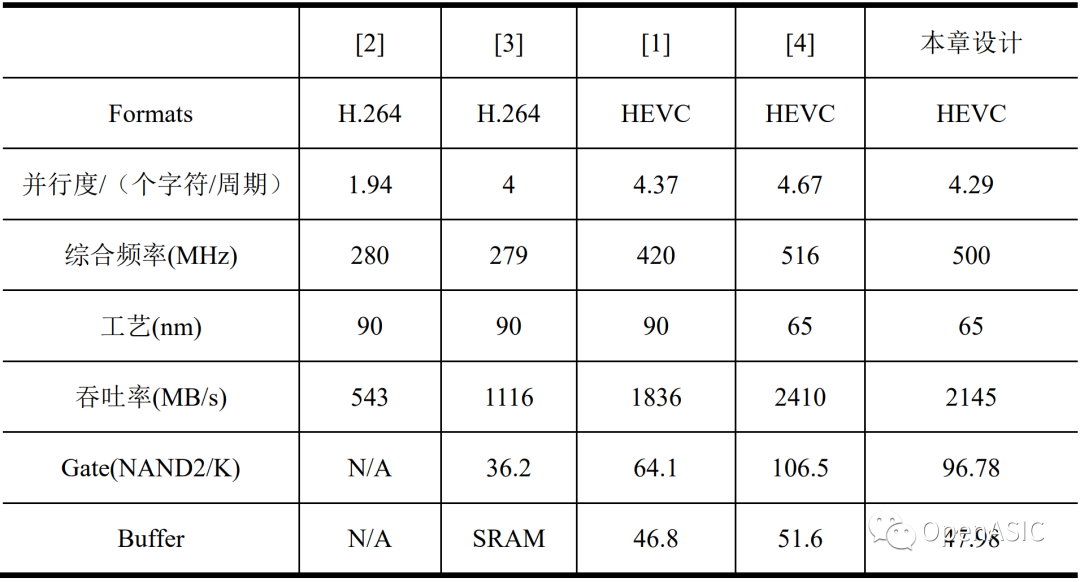

下表將本設計與其他已有研究進行了對比,本設計參考了部分并行技術,實際測試結果每周期能處理4.29個字符,綜合頻率進一步提升使得吞吐率很高。

表2

熵解碼的VLSI設計

下圖給出了熵解碼模塊的架構,由前文分析可知包括“判斷語法元素”、“更新上下文”、“算術解碼”和“反二值化”模塊,此外實際的熵解碼碼流輸入需要滿足一定的條件,因此這里需要額外的“碼流輸入”模塊控制輸入碼流。

表3

輸入碼流部分

解碼過程判斷解碼是LPS字符還是MPS字符的關鍵變量是區間范圍Range和偏移量Offset值。在解碼過程需要不斷輸入碼流,因此輸入碼流部分需要建立一個碼流寄存器,在初始化過程一次移入9比特碼流給Offset設置初始值,接著根據算術解碼過程產生的是否輸入碼流以及輸入多少比特碼流信號輸入碼流重整Offset。

判斷語法元素模塊

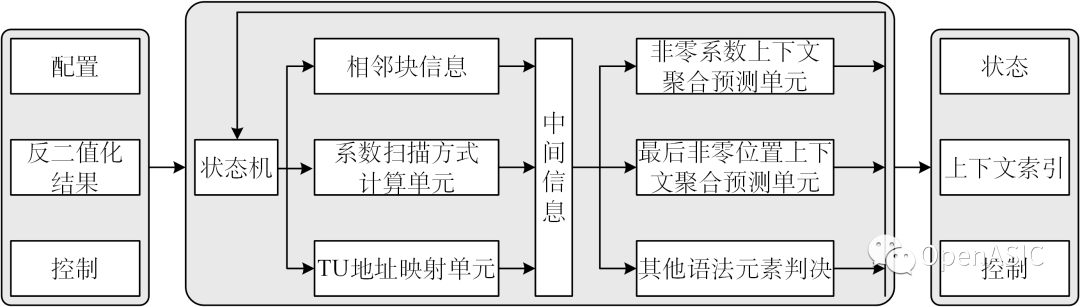

判斷語法元素模塊的功能是根據已經解析的語法元素,判斷接下來的語法元素種類,并且為其各個二進制字符分配上下文索引。因此此模塊的輸入包括:(1)此碼流配置信息,如編碼的原視頻的分辨率、編碼CTU大小等;(2)已解析語法元素;(3)控制信息,控制信息有是否初始化標志、輸入碼流狀態標志兩種。為了能夠并行處理,判斷語法元素部分對語法元素進行了聚合,即一個時鐘周期內預測多個語法元素種類并分配上下文索引。此模塊的架構如下圖11所示。

圖11

更新上下文模塊

此模塊功能較為簡單,是用寄存器實現的三讀三寫存儲器,每周期最多同時更新三個上下文,輸入為判斷語法元素模塊生成的上下文索引,以及算術解碼引擎解析出的上下文,輸出的是更新后的上下文,用于輸入算術解碼引擎。

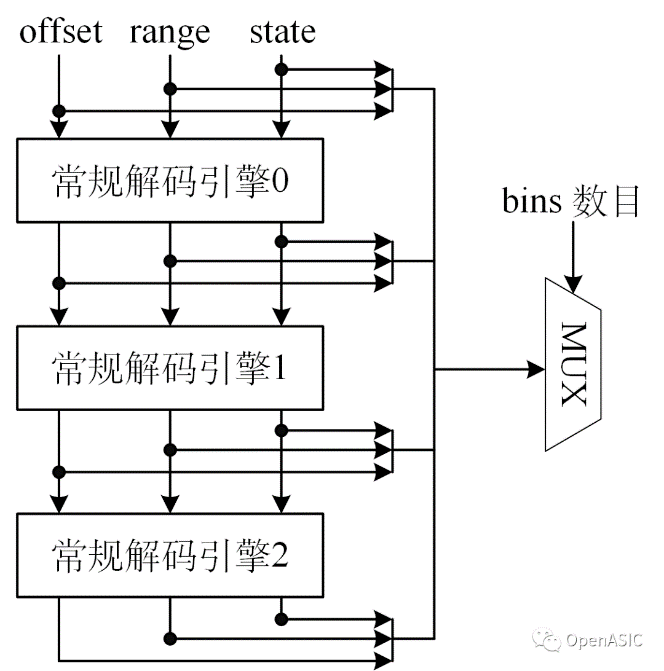

算術解碼模塊

此模塊實現常規解碼、旁路解碼和終端解碼三種解碼引擎。對于常規解碼,由于前級模塊均可以每周期處理多個字符,因此這里采用了三個算術解碼引擎級聯進行并行,如下圖12所示,最多同時解碼三個常規模式的字符。

圖12

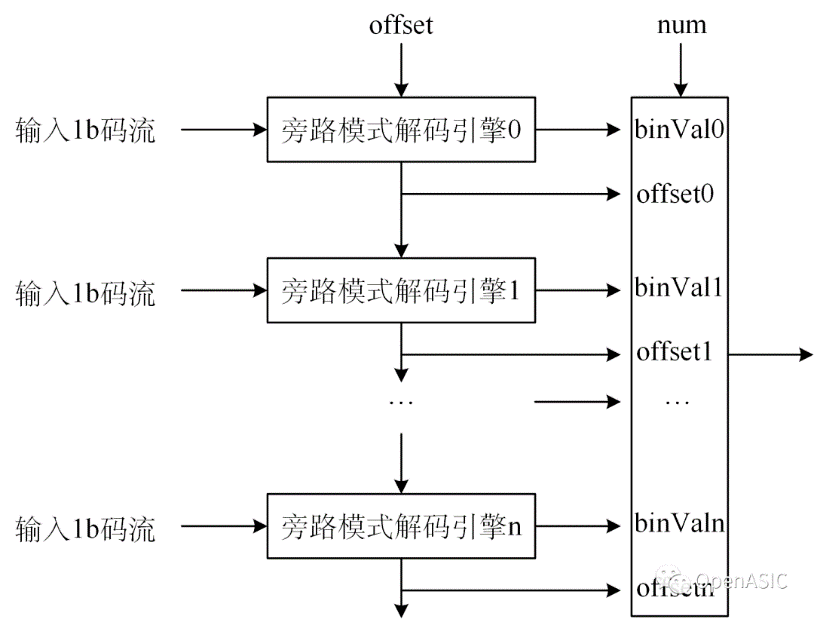

旁路模式字符解碼過程相對較為簡單,因此可以同時解碼多個字符而不會引入新的關鍵路徑。旁路模式解碼引擎的并行與常規模式的并行類似,直接進行級聯,再由輸入需要解碼字符數目控制Offset值的更新即輸入解碼字符即可,架構圖如下圖13所示。

圖13

反二值化模塊

反二值化模塊需要判斷每個語法元素的每個字符是否解析完畢,解析完畢即將接收到的二進制串反二值化還原出具體的語法元素。簡單的語法元素由于二值化方式簡單,只需要移位加即可還原語法元素,較為復雜且特殊的語法元素利用查找表進行實現。

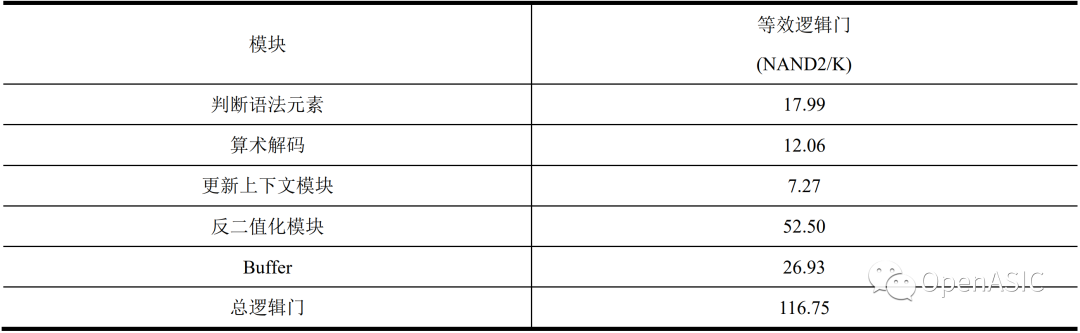

性能模塊

在TSMC65nm工藝下基于頻率333M對熵解碼做了綜合,綜合結果如下表4所示。

表4

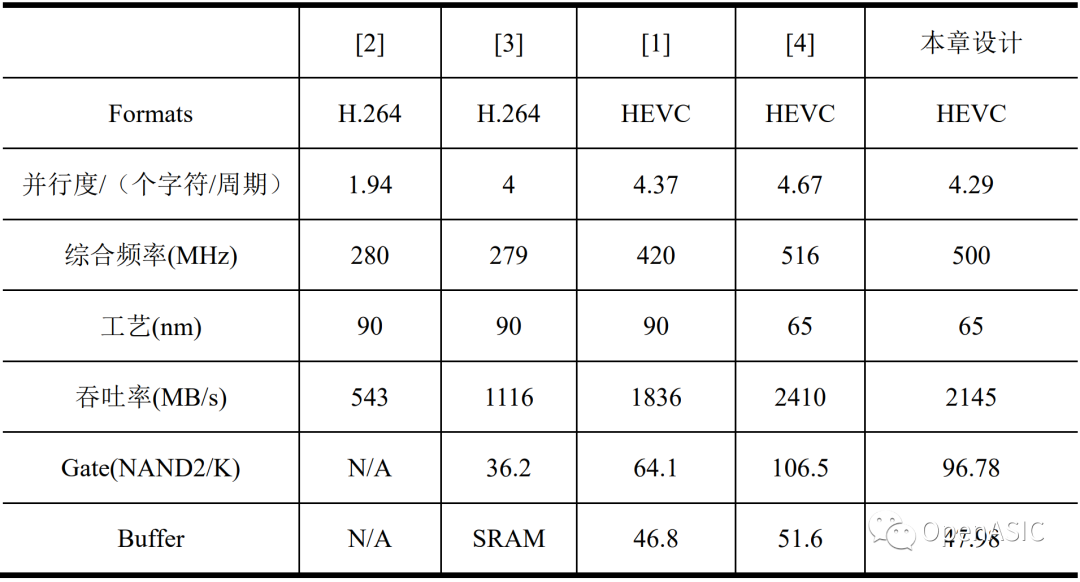

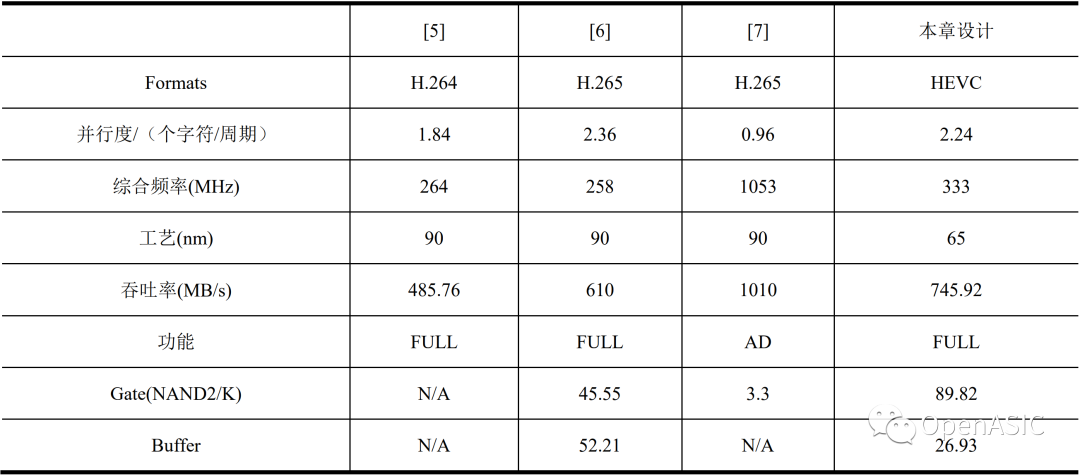

同時將本設計與其他已有設計進行了對比,對比結果如下表所示,本設計能夠實現2.24個字符/周期的并行解碼。

表5

參考文獻:

[1]Zhou D, ZhouJ, Fei W, et al.Ultra-high-throughput VLSI architecture of H. 265/HEVC CABACencoder for UHDTV applications[J].IEEE Transactions on circuits and systems forvideo technology, 2014, 25(3):497-507.

[2] DingL F, Chen W Y, Tsung P K, et al.A 212MPixels/s 4096× 2160p multiviewvideo encoder chip for 3D/quad HDTV applications[A].2009 IEEE InternationalSolid-State Circuits Conference-Digest of Technical Papers[C].IEEE,2009:154-155,155 a.

[3]FeiW, Zhou D, Goto S.A 1 Gbin/s CABAC encoder forH. 264/AVC[A].2011 19th European Signal Processing Conference[C].IEEE,2011:1524-1528.

[4] LiW, Yin X, Zeng X, et al.A VLSI Implement of CABAC Encoder for H.265/HEVC[A].2018 14th IEEE International Conference on Solid-State andIntegrated Circuit Technology (ICSICT)[C].IEEE, 2018:1-3.

[5]LiaoY H, Li G L, Chang T S.A highly efficient VLSI architecture for H. 264/AVClevel 5.1 CABAC decoder[J].IEEE transactions on circuits and systems for videotechnology, 2011, 22(2):272-281.

[6] ZhaoY, Zhou J, Zhou D, et al.A 610 Mbin/s CABACdecoder for H. 265/HEVC level 6.1 applications[A].2014 IEEE InternationalConference on Image Processing (ICIP)[C].IEEE, 2014:1268-1272.

[7] ZhouJ, Zhou D, Zhang S, et al.A Variable-Clock-Cycle-Path VLSI Design of BinaryArithmetic Decoder for H. 265/HEVC[J].IEEE Transactions on Circuits and Systemsfor Video Technology, 2016, 28(2):556-560.