本系列主要介紹視頻編解碼芯片的設(shè)計(jì),以HEVC視頻編碼標(biāo)準(zhǔn)為基礎(chǔ),簡要介紹編解碼芯片的整體硬件架構(gòu)設(shè)計(jì)以及各核心模塊的算法優(yōu)化與硬件流水線設(shè)計(jì)。本文介紹視頻編碼芯片的敏佳架構(gòu)設(shè)計(jì)思想和XK265 編解碼器的層次結(jié)構(gòu)。

相比于其他應(yīng)用,視頻編解碼的一大特點(diǎn)是對(duì)于實(shí)時(shí)性的要求極高,而軟件通常難以達(dá)到這一目標(biāo),因此幾乎所有相關(guān)設(shè)備,如監(jiān)控探頭、攝像機(jī)、手機(jī)和計(jì)算機(jī)等,都會(huì)配備硬編硬解芯片。而不同的設(shè)備平臺(tái)對(duì)于視頻編解碼的需求是迥然不同的,即便是同一設(shè)備平臺(tái),在不同的應(yīng)用場景下,其對(duì)于視頻編解碼的需求也不盡相同。不同的應(yīng)用需求,就要求視頻編解碼架構(gòu)能夠敏捷化地進(jìn)行配置。

1敏捷架構(gòu)

軟件算法在架構(gòu)和行為上不會(huì)考慮硬件實(shí)現(xiàn)中的相應(yīng)限制,往往難以在硬件平臺(tái)上發(fā)揮出原有的表現(xiàn)。而硬件算法方面,單個(gè)模塊的研究成果在架構(gòu)和行為上若不考慮整體實(shí)現(xiàn)時(shí)的系統(tǒng)限制,也往往難以在整體架構(gòu)中發(fā)揮出原有的表現(xiàn)。

從整體系統(tǒng)出發(fā),為了能夠盡可能地優(yōu)化面積、時(shí)序和功耗等指標(biāo),并且能夠針對(duì)不同的編解碼需求靈活地配置系統(tǒng),有必要采用一種敏捷的芯片架構(gòu)。這里的“敏捷”是一種設(shè)計(jì)理念,可以理解為一種可重構(gòu)性、可配置性,并且分為靜態(tài)和動(dòng)態(tài)兩類。

靜態(tài)是指對(duì)尚未生產(chǎn)的芯片進(jìn)行配置,以改變芯片所支持的功能集合,并進(jìn)而改變芯片的面積、(最高)頻率、功耗、(最高)質(zhì)量和(最高)性能等指標(biāo)。其主要意義在于可以敏捷地針對(duì)不同檔次的平臺(tái)提供不同檔次的芯片,從而達(dá)到效益的最大化。相比于重新設(shè)計(jì)一個(gè)芯片,靜態(tài)敏捷設(shè)計(jì)能夠有效地減少芯片的NRE (Non-Recurring Engineering) 成本和TTM (Time To Market)周期,而這對(duì)于芯片量產(chǎn)來說是至關(guān)重要的。

動(dòng)態(tài)是指對(duì)已經(jīng)生成的芯片進(jìn)行配置,以改變芯片所執(zhí)行的當(dāng)前功能,并進(jìn)而改變編碼的(工作)頻率、(工作)功耗、(工作)質(zhì)量和(工作)性能等指標(biāo)。其主要意義在于可以動(dòng)態(tài)地針對(duì)不同檔次的場景提供不同檔次的行為,從而達(dá)到功能的最大化。相比于只有某個(gè)單一功能,動(dòng)態(tài)敏捷設(shè)計(jì)能夠向客戶提供質(zhì)量與性能在不同比重上的權(quán)衡,而這對(duì)于芯片使用來說是至關(guān)重要的。

2可配置的模塊設(shè)計(jì)

編解碼器的主要模塊有FTH(讀取像素)、RMD(粗略模式估計(jì))、IME(整像素運(yùn)動(dòng)估計(jì))、FME(分像素運(yùn)動(dòng)估計(jì))、RDO(率失真優(yōu)化)、REC(重建)、DBF(方塊濾波)、SAO(樣點(diǎn)自適應(yīng)補(bǔ)償)、E_C(熵編碼)、E_D(熵解碼)、DMP(寫出像素)等。

豐富的可配置項(xiàng)對(duì)于敏捷架構(gòu)設(shè)計(jì)非常重要。下表1總結(jié)了敏捷架構(gòu)下,部分底層模塊的靜態(tài)和動(dòng)態(tài)可配置參數(shù)。

表1

|

模塊名稱 |

靜態(tài)可配置 |

動(dòng)態(tài)可配置 |

|

RMD |

1. 引擎數(shù)量 |

1. 被搜索的PU大小 |

|

IME |

1. 陣列大小 |

1. 被搜索的圖案 |

|

FME |

1. 引擎數(shù)量 |

1. 被搜索的PU大小 |

|

RDO |

1. 引擎大小 |

1. 被遍歷的幀內(nèi)預(yù)測模式數(shù)量 |

3 XK265編解碼器

XK265是一款具有敏捷架構(gòu)的視頻編解碼器,其層次結(jié)構(gòu)能夠高效地配置視頻編解碼器的行為。基于敏捷的芯片架構(gòu),可以很容易地定制單一編碼器、單一解碼器或復(fù)合編解碼器,以及支持單一I幀版本或支持I幀和P幀版本的不同IP核,同時(shí)也可以定制生成不同性能指標(biāo)、面積指標(biāo)、壓縮率指標(biāo)的專用編碼器IP核。

作為一款具有敏捷架構(gòu)的視頻編解碼器,XK265 RTL已經(jīng)包含了12個(gè)變種,分別是X001 CDC I、X001 CDC P、X001 ENC I、X001 ENC P、X001 DEC I、X001 DEC P、K001 CDC I、K001 CDC P、K001 ENC I、K001 ENC P、K001 DEC I和K001 DEC P。其中,001表示第一個(gè)版本,以HEVC標(biāo)準(zhǔn)為依托;X表示針對(duì)ASIC平臺(tái),K表示針對(duì)FPGA平臺(tái);CDC表示支持編解碼(encoder和decoder),ENC表示支持編碼(encoder),DEC表示支持解碼(decoder);I表示支持幀內(nèi)幀、P表示同時(shí)支持幀內(nèi)幀和幀間幀。

以X001CDC P、K001 ENC P和K001 DEC P作為敏捷架構(gòu)的IP定制的例子,下表2總結(jié)了相關(guān)的參數(shù)。

表2

|

型號(hào) |

X001 CDC P |

K001 ENC P |

K001 DEC P |

|

目標(biāo)頻率 |

800MHz |

140MHz |

120 MHz |

|

性能 |

4K@30fps |

4K@30fps |

4K@30fps |

|

流水線 |

五級(jí) |

七級(jí) |

七級(jí) |

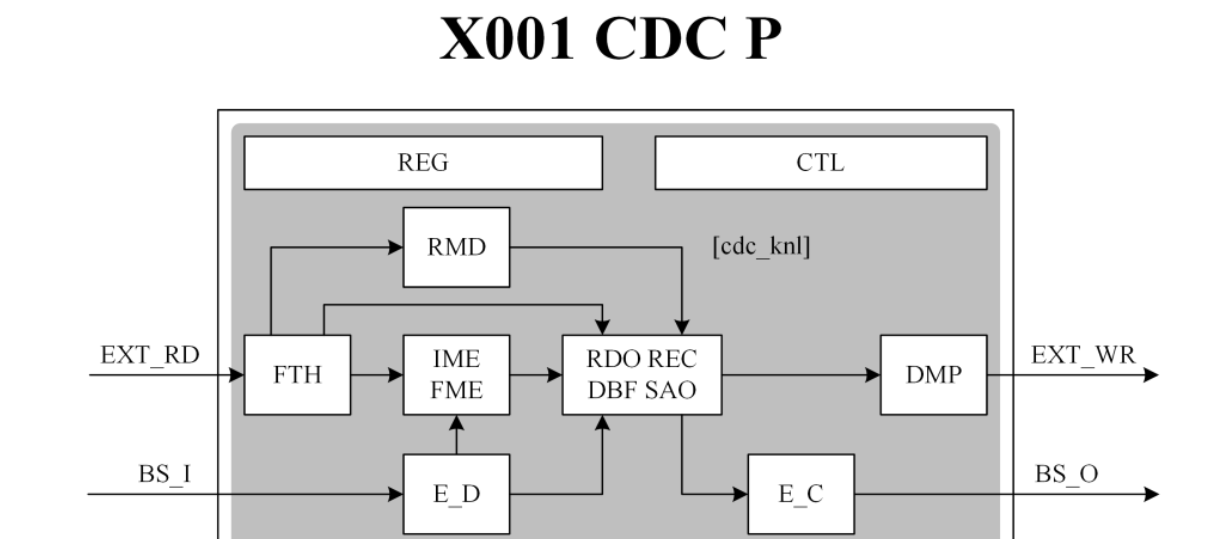

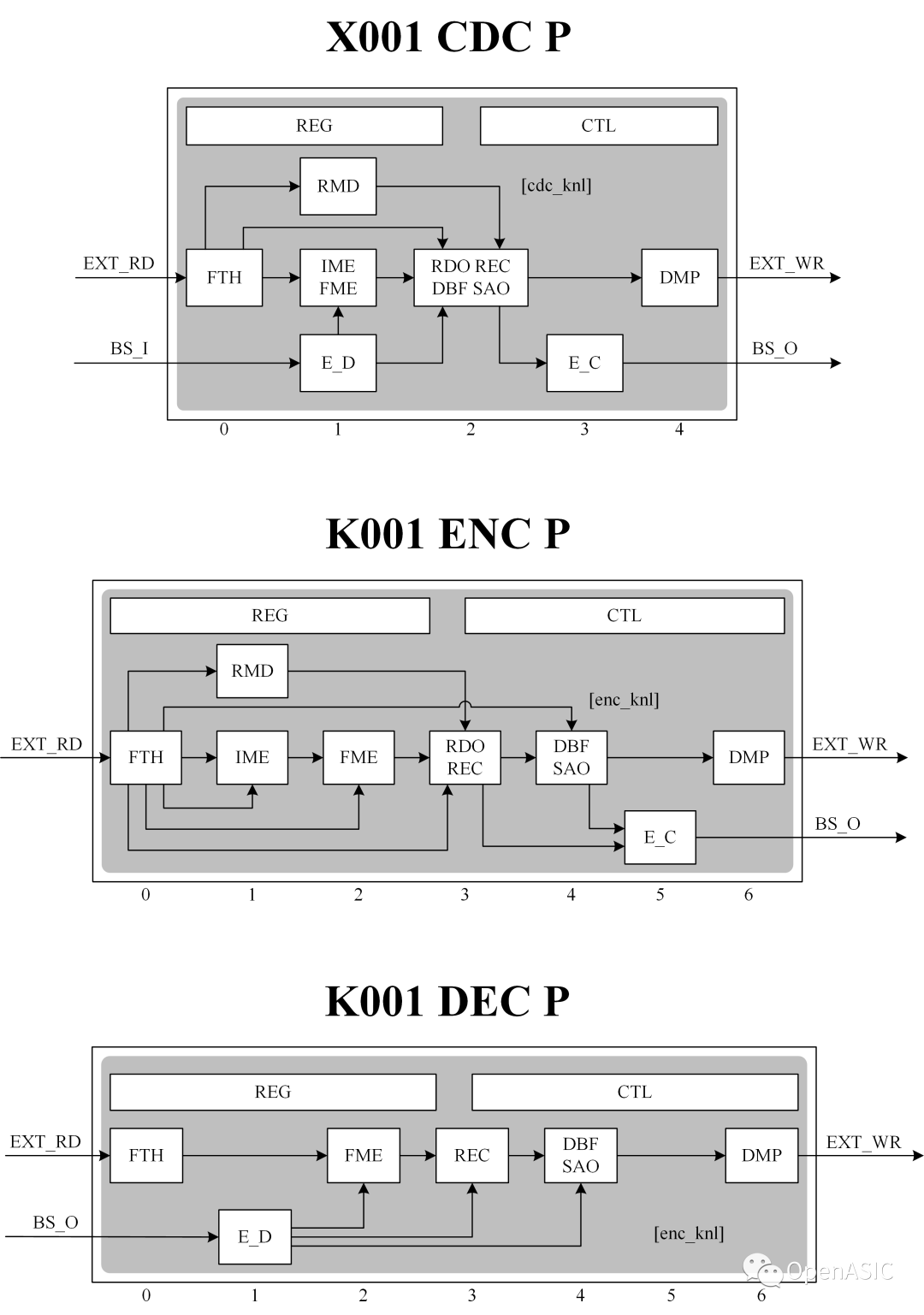

其中,X001CDC P是一款面向于ASIC平臺(tái)的極低代價(jià)、較高性能、較高質(zhì)量的視頻編解碼器;K001 ENC P是一款面向于FPGA平臺(tái)的極低代價(jià)、極高性能、中下質(zhì)量的視頻編碼器;K001 DEC P是一款面向于FPGA平臺(tái)的極低代價(jià)、極高性能的視頻解碼器。它們的架構(gòu)如下圖1所示。

圖1