視頻編解碼芯片設計原理----08 環路濾波

本系列主要介紹視頻編解碼芯片的設計,以HEVC視頻編碼標準為基礎,簡要介紹編解碼芯片的整體硬件架構設計以及各核心模塊的算法優化與硬件流水線設計。

本文將首先介紹環路濾波的基礎知識,對H.265/HEVC標準的兩種濾波器進行概述。然后分別給出兩種濾波器的硬件實現方案,并與已有的硬件實現工作進行對比。

概述

H.265/HEVC的環路濾波技術包含去方塊濾波(DBF,De-Blocking Filter)和樣點自適應補償(SAO,SampleAdaptive Offset)兩種濾波器,二者可以合稱為環路濾波器。DBF先對重建圖像進行處理以改善方塊效應(blocking effect),處理后的像素經由SAO進一步處理以改善振鈴效應。

基于塊的混合編碼算法會導致塊與塊之間的不連續性,會影響幀間預測的效率和視覺觀感。為了改善這類問題,在反量化后會引入環路濾波來對圖像進行進一步處理。經過濾波的重建圖像一方面會作為顯示輸出,另一方面會作為參考幀,繼續參與后續幀的運動補償,因而環路濾波能夠有效地提升視頻的主客觀水平。

01

去方塊濾波 (DBF)

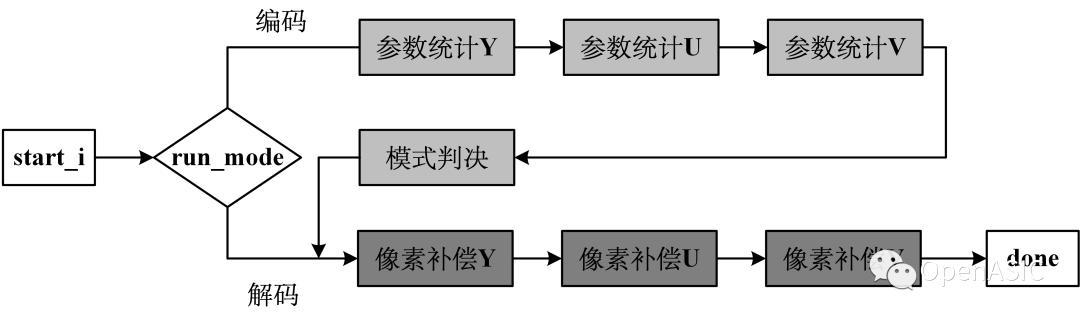

H.265/HEVC去方塊濾波器僅對亮度和色度像素的8×8塊邊界進行濾波,并且濾波邊界必須是PU或TU的邊界(圖像邊界除外)。濾波操作以左右(垂直邊界)或上下(水平邊界)的兩個相鄰4×4塊為單位,這兩個4×4塊分別稱為P塊和Q塊,如下圖1所示。

圖1

去方塊濾波大致可分為濾波決策和濾波操作。

濾波決策需要根據邊界的實際情況,判斷是否濾波以及采用何種濾波強度。

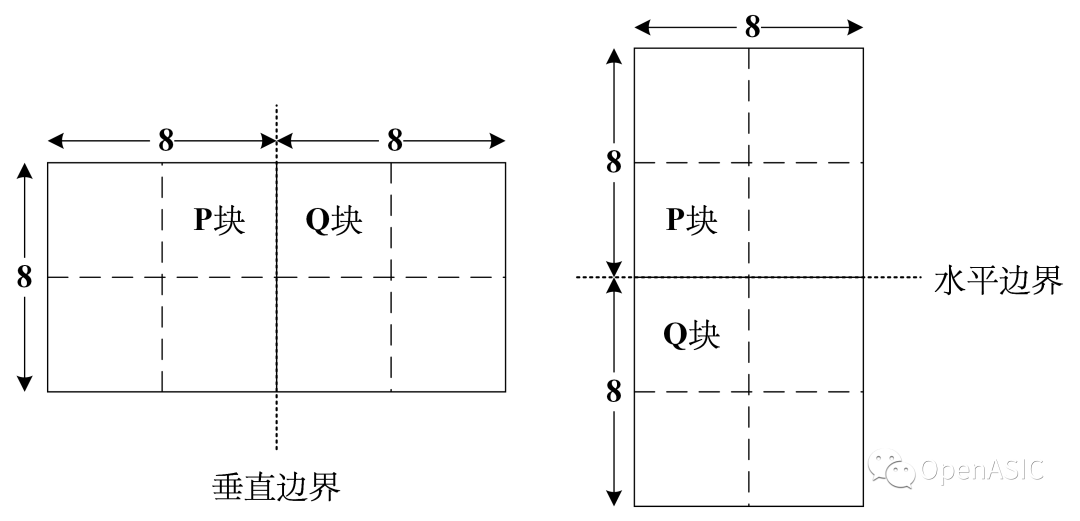

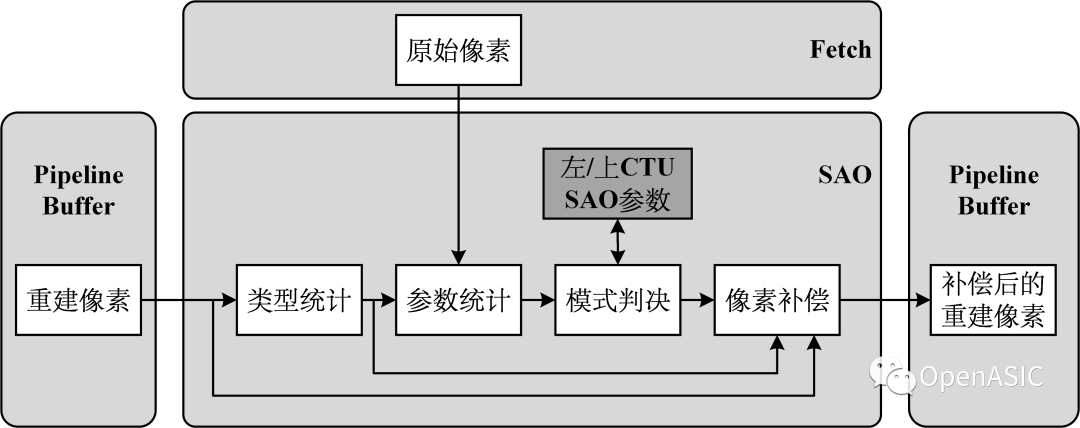

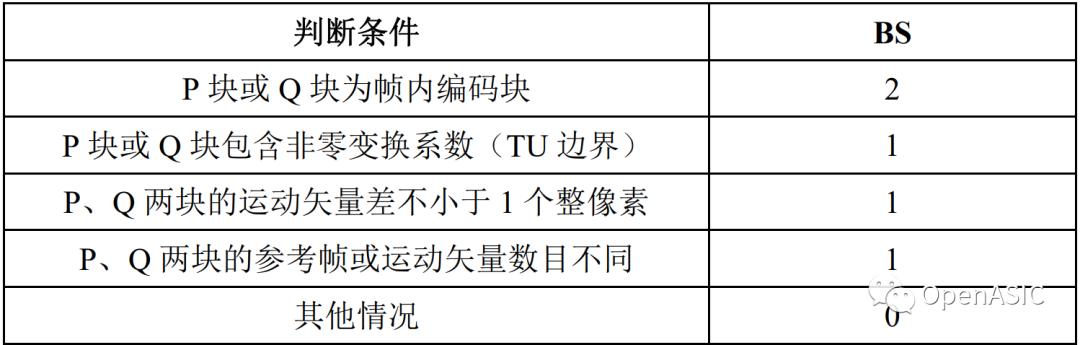

對于待濾波邊界,要根據邊界兩側像素的特征來判斷濾波邊界強度(BS,Boundary Strength)。具體判斷條件如表1所示。邊界強度為0則不進行濾波,而邊界強度大于0的時候,還需要進一步判斷是否進行濾波,也就是是否開啟濾波開關。

表1 邊界強度判斷條件

由于人眼對于平坦區域中的不連續邊界更加敏感,而對于像素本就變化劇烈的非平坦區域,人眼可能無法識別到不連續邊界,此時若進行濾波操作,會減弱像素變化的劇烈程度,反而會引入失真。所以只有當區域的變化劇烈程度小于某個閾值時,才開啟濾波開關。

在開啟濾波開關的情況下,H.265/HEVC中色度分量只有一種濾波模式,但是亮度分量具有強濾波和弱濾波兩種模式,因此還需要對亮度分量的濾波強度進行判斷,主要也與像素值變化的劇烈程度。當較為平坦的時候,塊效應更加明顯,需要進行強濾波來實現更大范圍和更大幅度的修正;而在相對非平坦的區域則進行弱濾波,防止過度修正導致失真。

濾波操作包含了3個部分:亮度強濾波、亮度弱濾波、色度濾波。亮度強濾波需要用到邊界兩側的4個像素,修正范圍包括邊界兩側各3個像素,并且對P塊和Q塊像素的處理是對稱的。亮度弱濾波中,P塊或Q塊中的修正范圍可能為0~2個像素點,需要根據像素值進行判斷,且P塊和Q塊的判斷是相互獨立的。色度濾波則較為簡單,只要邊界強度為2,且濾波開關打開,就對色度分量進行濾波,無需其他判斷條件。并且色度濾波只有一種模式,僅修正邊界兩側各1個像素點。

濾波操作相關的判斷公式及計算公式,可查閱HEVC標準[1]第8.7.2.5節,此不贅述。

樣點自適應補償 (SAO)

樣點自適應補償從像素領域入手降低振鈴效應,簡單來說就是對解碼像素的波谷位置添加正補償,波峰位置添加負補償,以此減小像素失真。

SAO首先對每個像素進行類別劃分,并計算得到每種類別的補償值(offset),然后通過計算每種類別的率失真情況得到最優類別,再將最優類別對應的補償值加到相應的像素點上。SAO包括邊界補償(EO,Edge Offset)和帶狀補償(BO,Band Offset)兩種模式。

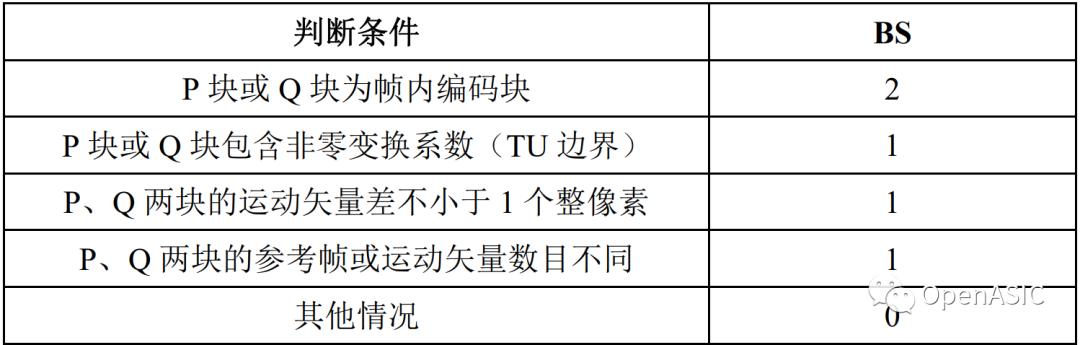

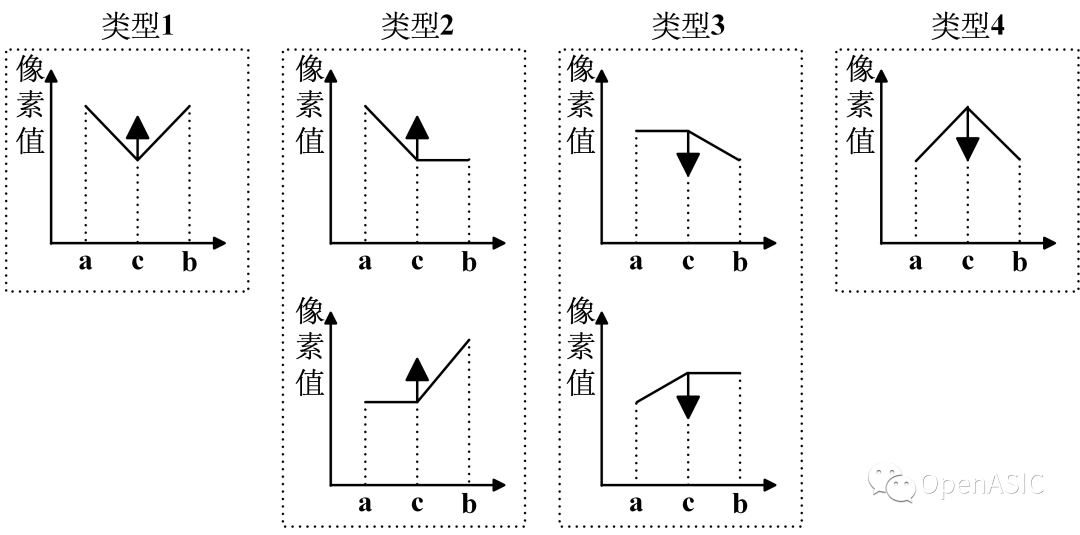

邊界補償模式通過比較當前像素值與相鄰像素值的大小對當前像素進行歸類,然后對同類像素補償相同數值。根據當前像素與周圍像素選取的不同方向,可分為水平(EO_0)、垂直(EO_1)、斜對角135°(EO_2)和斜對角45°(EO_3)共4種模式,如圖2所示。而每種邊界補償模式下,又包括了5種子類型。其中4種子類型如圖3所示,其他情況則屬于第5種子類型。

圖2

圖3

帶狀補償模式是基于像素值大小進行分類。將像素范圍平均分為32個帶,編號為0~31。以常規的8比特量化深度為例,其像素值分布在0~255之間,則每個帶包含8個像素值。不同的帶具有不同的補償值。帶狀補償模式下,以連續4個帶為一組(共29組)進行模式判決。之所以為BO模式只選擇了4個連續的帶作為最優判決結果,是因為一個CTB中像素值的分布區域是有限的,4個連續的帶可以覆蓋大部分像素點。判決得到最優BO模式后,只需將四條連續帶的起始帶編號以及相應的4個補償值作為BO模式信息參與編碼,從而大大減低碼率需求。

另外,SAO也存在Merge模式。若當前塊采用Merge模式,則可復用相鄰塊(左側或上方)的SAO參數,從而減小編碼SAO參數的復雜度。

DBF VLSI實現

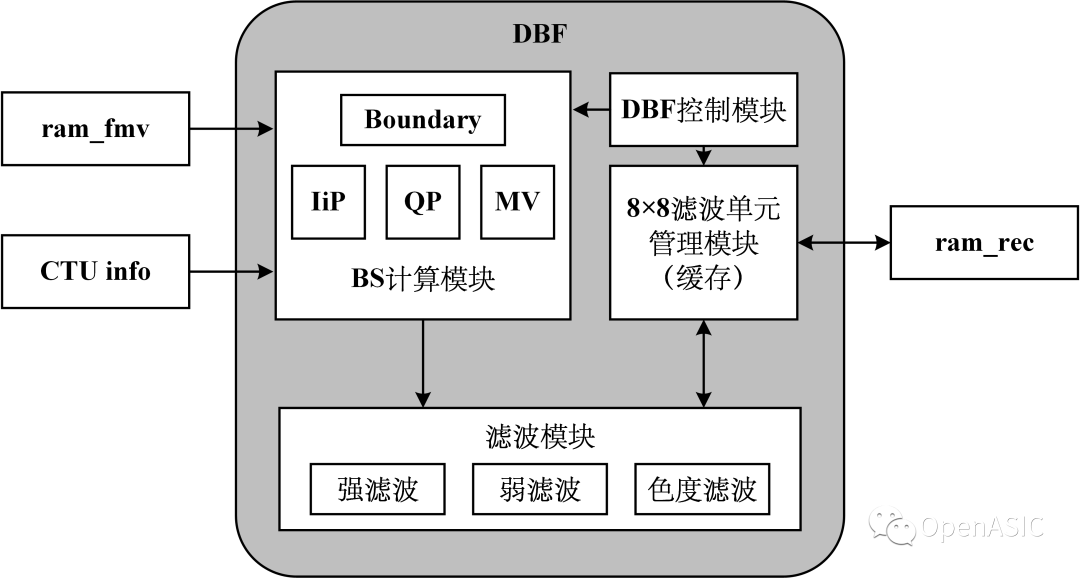

圖4是DBF的頂層架構圖。

圖4

各模塊的功能如下:

① DBF控制模塊:實現濾波任務的發布,控制濾波單元的遍歷、顏色通道以及外部RAM的交互接口,包括ram_fmv(P幀的運動矢量信息)和ram_rec(濾波前的重建像素),取回的數據分別傳輸給BS 計算模塊和8×8 濾波單元管理模塊。

② BS計算模塊:接收CTU信息后,根據濾波單元的位置和當前邊界兩側的編碼參數計算邊界強度,同時生成濾波判決所需的參數β和。

③ 8×8濾波單元管理模塊:負責濾波單元的構建,根據濾波單元的位置信息輸出4×8個像素值,其內部是一組緩存。

④ 濾波模塊:負責濾波操作,其中包括三類濾波器并行執行,通過判決選擇其中之一輸出。處理完兩個垂直邊界后,將輸出轉置后再次進行相同的操作處理水平邊界。

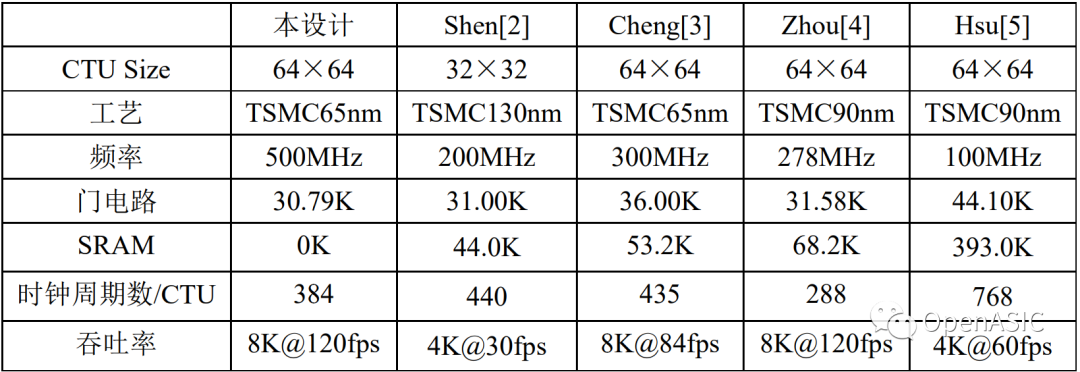

表2將本文實現的結果與已有工作進行了對比。本文提出的基于8×8濾波單元設計,無需使用SRAM存儲濾波垂直邊界和水平邊界的中間像素,大大降低了片上資源代價。最終本文實現的DBF硬件架構,能夠滿足8K@120fps高吞吐率的視頻實時應用。

表2 DBF硬件實現結果對比

SAO VLSI實現

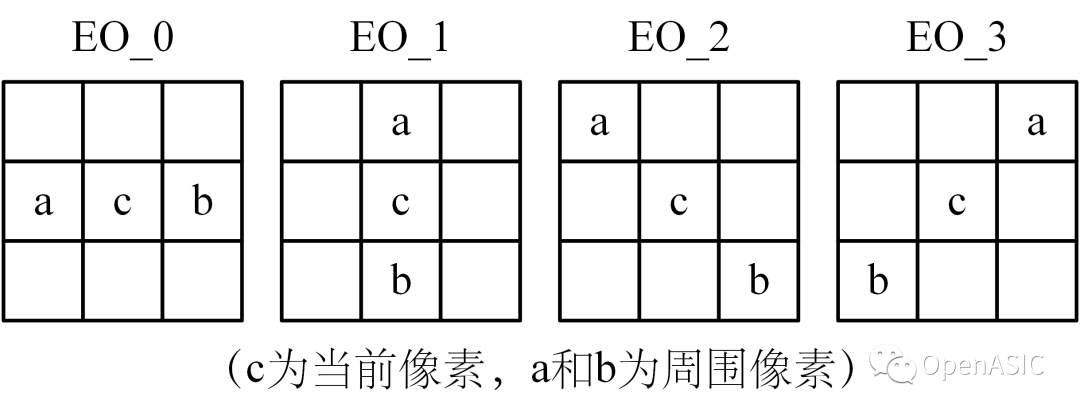

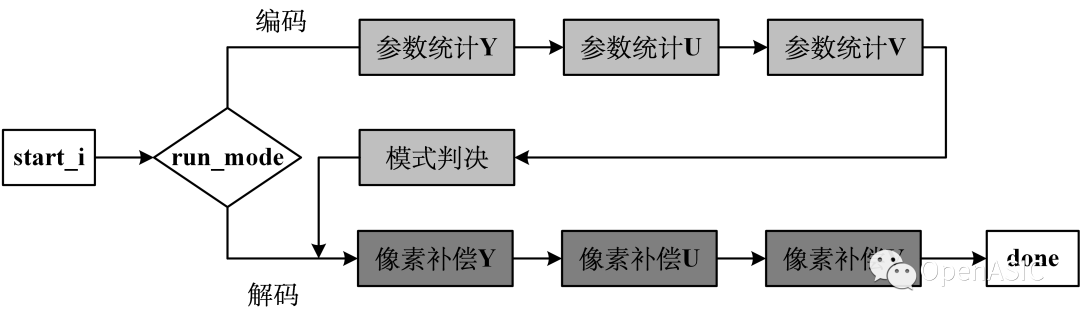

編碼端的SAO主要包括三個流程,參數統計、模式判決、像素補償。參數統計是統計塊內部重建像素所屬的SAO分類,用于后續的模式判決以及像素補償;模式判決過程是根據前端統計結果,計算每個類型的補償值及率失真代價,利用RDO(Rate-Distortion Optimization)公式,選擇最優的SAO分類及其補償值;最后需要根據前端模式判決結果,補償重建像素,完成輸出。而解碼端則只需要根據傳遞的SAO信息對重建像素進行補償即可。

為了適應編碼和解碼的硬件設計,本節提出可配置的SAO狀態機設計,根據需求可配置成編碼或者解碼方案。圖5為狀態機轉換圖及算法流程圖,SAO模塊收到開始信號start_i后,即執行SAO算法流程,根據配置信號run_mode可以進行編碼或者解碼的狀態機轉換。

圖5

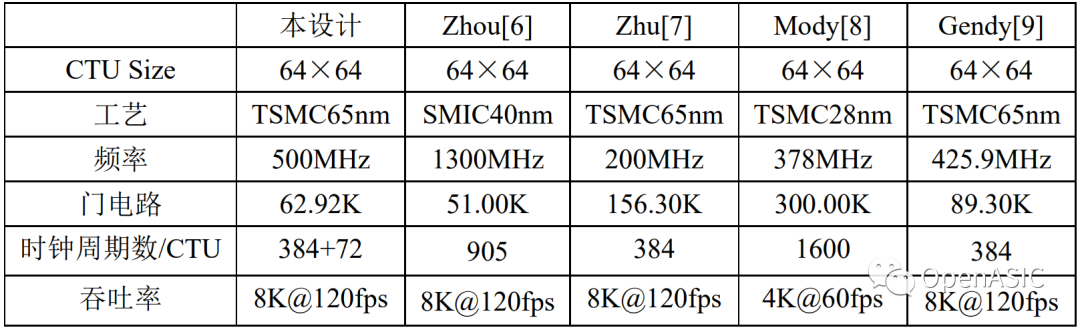

由于SAO的流程較清晰,且參數統計、模式判決、像素補償三個過程間具有很強的數據依賴關系,因此本節提出的SAO架構中三個過程順序執行,通過狀態機控制流程,頂層架構如圖6所示。

圖6

表3和表4對本文工作與其他SAO硬件工作進行了對比。編碼端的對比結果顯示,本文提出的硬件代價相對較少,吞吐率較高,最高可滿足8K@120fps視頻實時應用。在解碼端SAO相關工作的對比中,本文提出的架構硬件代價相對較低,這得益于高效的SAO分類器。

表3 編碼端SAO硬件實現結果對比

表4 解碼端SAO硬件實現結果對比

參考文獻:

[1] ITU-T Recommendation H.265. Highefficiency video coding[S]. ITU-T, 2013.

[2] Shen W, Shang Q, Shen S, etal. A high-throughput VLSI architecture for deblocking filter in HEVC[C]. 2013IEEE International Symposium on Circuits and Systems (ISCAS2013). IEEE, 2013:673-676.

[3] Cheng W, Fan Y, Lu Y H, etal. A high-throughput HEVC deblocking filter VLSI architecture for 8k× 4kapplication[C]. 2015 IEEE International Symposium on Circuits and Systems(ISCAS). IEEE, 2015: 605-608.

[4] Zhou W, Zhang J, Zhou X, etal. A high-throughput and multi-parallel VLSI architecture for HEVC deblockingfilter[J]. IEEE Transactions on Multimedia, 2016, 18(6): 1034-1047.

[5] Le H H N, Bae J.High-Throughput Parallel Architecture for H. 265/HEVC Deblocking Filter[J]. J.Inf. Sci. Eng., 2014, 30(2): 281-294.

[6] Zhou J, Zhou D, Wang S, etal. A dual-clock VLSI design of H. 265 sample adaptive offset estimation for 8kultra-HD TV encoding[J]. IEEE Transactions on Very Large Scale Integration(VLSI) Systems, 2016, 25(2): 714-724.

[7] Zhu J, Zhou D, Kimura S, etal. Fast SAO estimation algorithm and its VLSI architecture[C]. 2014 IEEEInternational Conference on Image Processing (ICIP). IEEE, 2014: 1278-1282.

[8] Mody M, Garud H, Nagori S,et al. High throughput VLSI architecture for HEVC SAO encoding for ultra HDTV[C].2014 IEEE International Symposium on Circuits and Systems (ISCAS). IEEE, 2014:2620-2623.

[9] El Gendy S, Shalaby A, SayedM S. Low cost VLSI architecture for sample adaptive offset encoder in HEVC[C].2016 IEEE Computer Society Annual Symposium on VLSI (ISVLSI). IEEE, 2016:170-175.

[10]Baldev S, Shukla K, Gogoi S,et al. Design and implementation of efficient streaming deblocking and saofilter for hevc decoder[J]. IEEE Transactions on Consumer Electronics, 2018,64(1): 127-135.

[11]Zhu J, Zhou D, He G, et al. Acombined SAO and de-blocking filter architecture for HEVC video decoder[C].2013 IEEE International Conference on Image Processing. IEEE, 2013: 1967-1971.

[12]Kim H M, Ko J G, Park S. Anefficient architecture of in-loop filters for multicore scalable hevc hardwaredecoders[J]. IEEE Transactions on Multimedia, 2017, 20(4): 810-824.